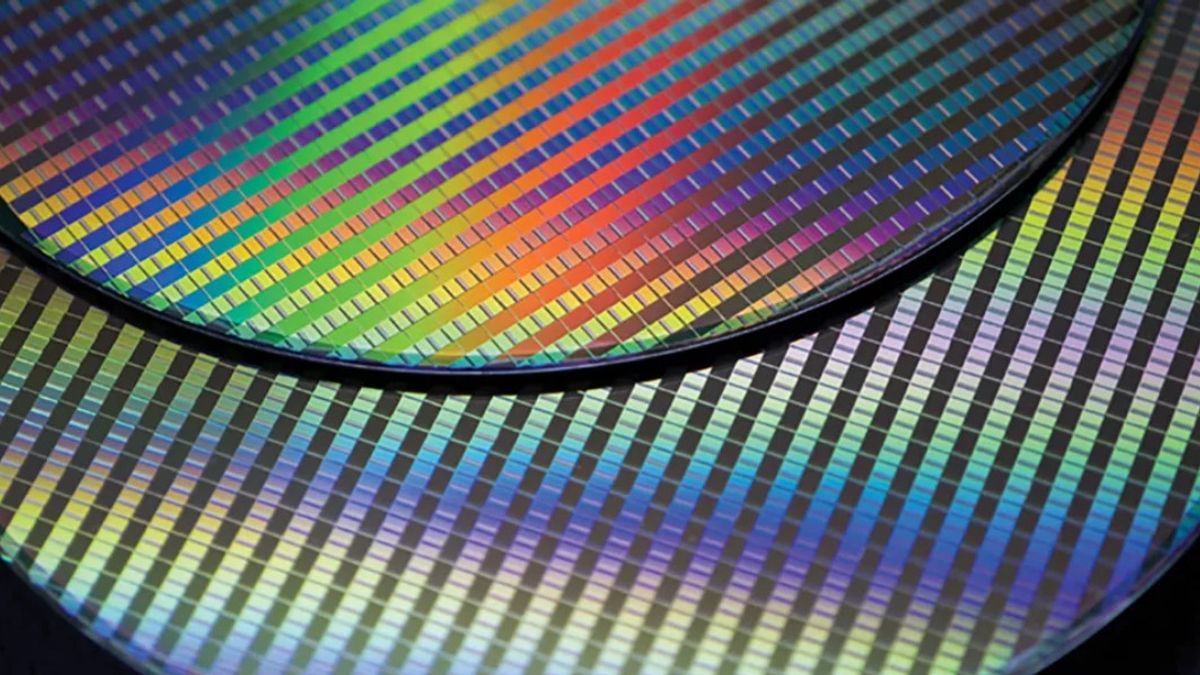

ジャカルタ - 台湾半導体製造公司(TSMC)は最近、2026年に顧客への出荷を開始する予定の2ナノメートル(nm)プロセスでチップを製造する計画に関する最新情報を提供しました。

TSMCのCC Wei最高経営責任者(CEO)は最近、同社の2nmチップが、予想通り、現在のフィン電界効果トランジスタ(FinFET)構造からの変化を示すゲートオールアラウンドトランジスタ(GAA)に依存することを正式に確認した。

製造プロセスは、既存の極端紫外線リソグラフィー(EUV)にも依存し続け、開口数は0.33です。

この技術は、2024年末までにリスクステージ生産、2025年末にかけて大量生産(HVM)の準備が整う見込み。つまり、TSMCのお客様は2026年に最初の2nmベースのチップを受け取ることになります。

TSMCは一貫して2年ごとにプロセスノードの更新を提供し、その間に既存のノードの拡張およびカスタマイズされたバージョンを展開します。

しかし、TSMCは2nmプロセスに最初に取り組んだのはもちろんのこと、TSMCだけではなく、競合他社のいくつかは深刻な進歩を遂げています。IBMは昨年、最初の2nmチップを発売した。

IBMのブレークスルーは非常に重要です。メーカーは、2nmプロセスを使用して、人間の爪のサイズのチップに500億個の大きなトランジスタを収めることができると述べています。これは、IBMが2017年に発表した5nmプロセスよりも200億多くなっています。

すべての主要メーカーは、ゆっくりと小さなプロセスノードに向かっています。7nmから5nmへ、そして将来的には5nmから3nmへの移行により、性能と熱の面で大幅な改善がもたらされます。

トランジスタを小さくすると、消費電力が少なくなり、スペースが少なくなり、より小さなチップにより多くのコアを積み重ねることができるため、パフォーマンスが向上します。

同様に、2nmに切り替えると、今日のハードウェアを搭載したコンピューターでは想像できないパフォーマンスが得られますが、待つ必要があります。

TSMCは、新しいチップは2025年に量産を開始する予定であると述べているが、2026年後半より早くPCで見られる可能性は低い。2nmプロセスが成功した製品に含まれるまでには長い道のりがあります。

The English, Chinese, Japanese, Arabic, and French versions are automatically generated by the AI. So there may still be inaccuracies in translating, please always see Indonesian as our main language. (system supported by DigitalSiber.id)