ジャカルタ - 12月11日(土)にインテル社の研究チームは、今後10年間でコンピューティングチップの加速と縮小を支援すると考える作業を発表しました。これは、チップの一部を重ねて積み重ね合う技術を使用して行われます。

インテル・リサーチ・コンポーネントズ・グループは、サンフランシスコで開催された国際会議で論文に本研究を紹介しました。これらのシリコンバレーの企業は、最小かつ最速のチップを作る際にリードを取り戻すために取り組んでいます。

ここ数年、台湾半導体製造(TMSC)やサムスン電子などの競合他社に最速のチップを作ることに負けています。

インテルのパット・ゲルシンガー最高経営責任者(CEO)は、2025年までにその優位性を取り戻すことを目的とした商業計画を策定しているが、先週の土曜日に開始された研究作業は、インテルが2025年以降にどのように競争する計画の概要を提供している。

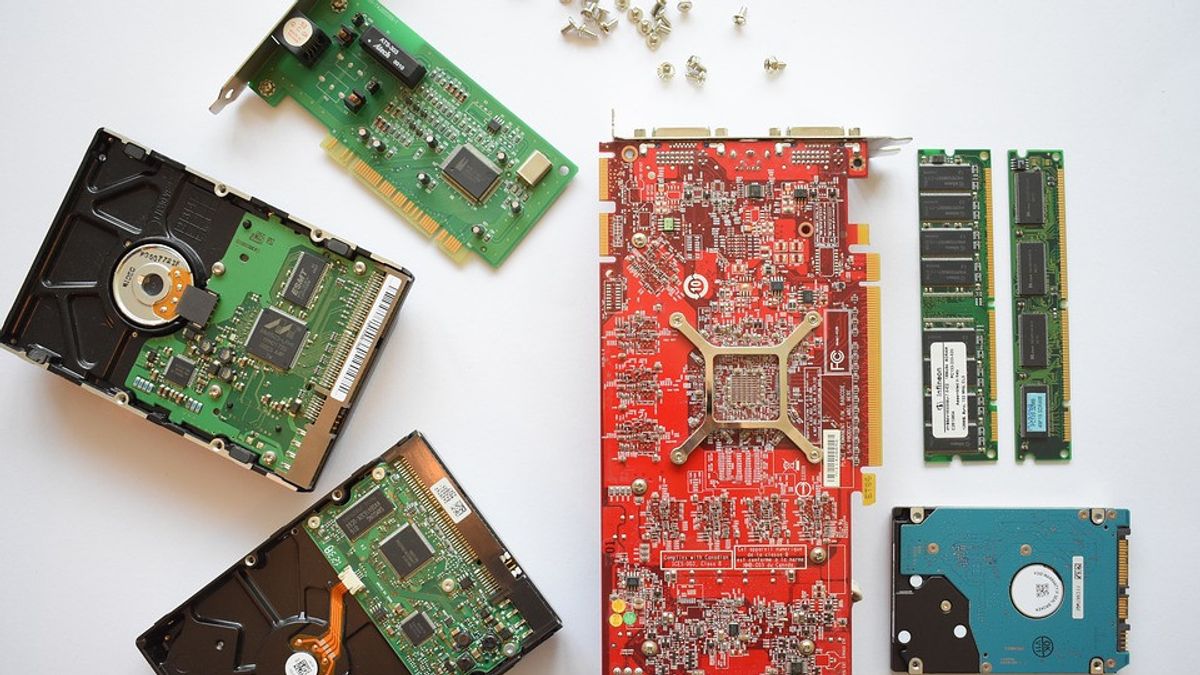

一つの方法として、インテルは、すべてのチップを2次元で1つの部分として作るのではなく、「タイル」または「チプレット」を3次元に積み重ねる方法です。インテルは土曜日に、積み重ねられたタイル間の接続を10倍に増やすことができる作業を実証しました。

しかし、おそらく先週の土曜日に実証された最大の進歩は、トランジスタを積み重ねる方法を示す研究論文でした - デジタルロジック1sと0を表すことによってチップの最も基本的なビルディングブロックを構成する小さなスイッチ - 互いの上に。

インテルは、この技術により、チップの所定の領域にパックできるトランジスタの数が30%から50%増加すると考えています。トランジスタの数を増やすことは、チップが過去50年間で一貫して速くなった主な理由です。

「デバイスを互いに直接積み重ねることで、我々はエリアを節約しています」と、インテル・コンポーネントズ・リサーチ・グループのディレクター兼シニア・プリンシパル・エンジニアのポール・フィッシャーはロイターのインタビューで語りました。

「相互接続の長さを短くし、エネルギーを節約し、費用対効果が高いだけでなく、より優れたパフォーマンスを実現しています」と彼は言いました。

The English, Chinese, Japanese, Arabic, and French versions are automatically generated by the AI. So there may still be inaccuracies in translating, please always see Indonesian as our main language. (system supported by DigitalSiber.id)