JAKARTA - Une équipe de recherche d’Intel Corp. a dévoilé samedi 11 décembre des travaux qui, selon eux, aideront à accélérer et à continuer à réduire les puces informatiques au cours des dix prochaines années. Cela se fait avec plusieurs technologies visant à empiler des parties de la puce les unes sur les autres.

Le groupe Intel Research Components a présenté le travail dans un document lors d’une conférence internationale tenue à San Francisco. Ces entreprises de la Silicon Valley s’efforcent de reprendre leur avance dans la fabrication des puces les plus petites et les plus rapides.

Au cours des dernières années, ils ont perdu à fabriquer les puces les plus rapides au profit de concurrents tels que Taiwan Semiconductor Manufacturing Co (TMSC) et Samsung Electronics Co Ltd.

Alors que le PDG d’Intel, Pat Gelsinger, a présenté un plan commercial visant à retrouver cet avantage d’ici 2025, les travaux de recherche lancés samedi dernier donnent un aperçu de la façon dont Intel prévoit de rivaliser au-delà de 2025.

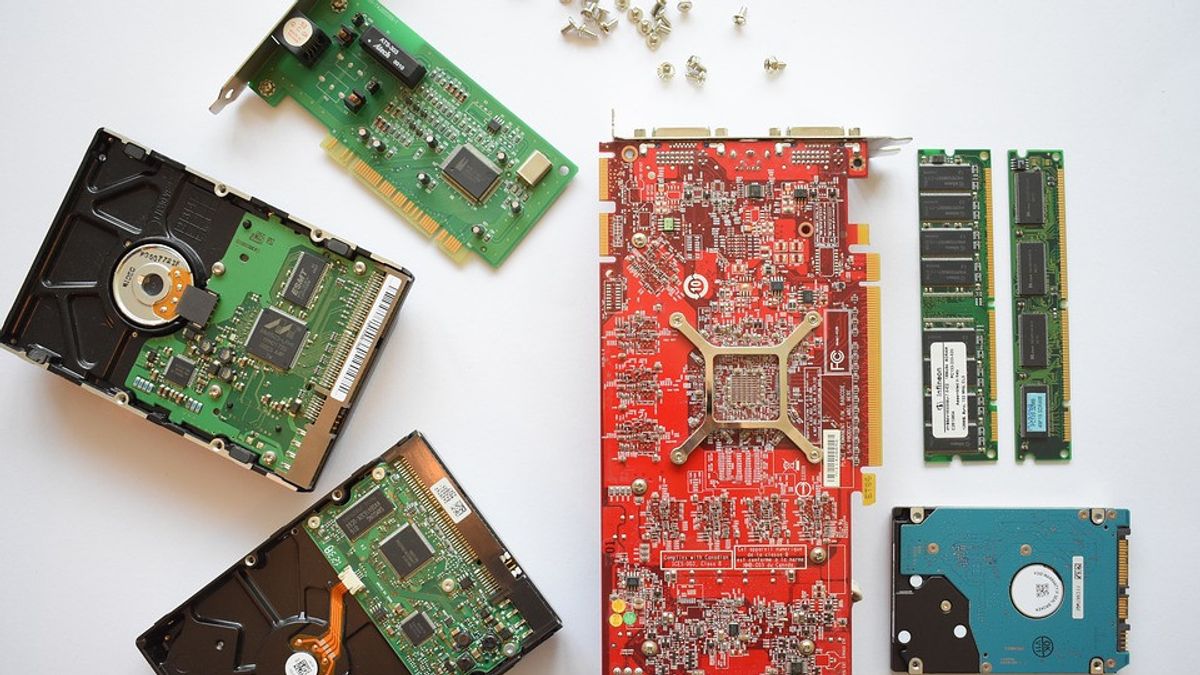

Une façon, Intel emballe plus de puissance de calcul dans les puces est d’empiler des « tuiles » ou des « chiplets » en trois dimensions plutôt que de fabriquer toutes les puces comme une seule pièce en deux dimensions. Intel a démontré samedi un travail qui pourrait permettre 10 fois plus de connexions entre les tuiles empilées, ce qui signifie que des tuiles plus complexes peuvent être empilées les unes sur les autres.

Mais peut-être que la plus grande avancée démontrée samedi dernier a été un document de recherche montrant comment empiler des transistors - les minuscules commutateurs qui constituent les blocs de construction les plus élémentaires des puces en représentant les logiques numériques 1 et 0 - les uns sur les autres.

Intel estime que la technologie entraînera une augmentation de 30% à 50% du nombre de transistors pouvant être emballés dans une zone donnée d’une puce. L’augmentation du nombre de transistors est la principale raison pour laquelle les puces sont constamment devenues plus rapides au cours des 50 dernières années.

« En empilant les appareils directement les uns sur les autres, nous économisons de la surface », a déclaré Paul Fischer, directeur et ingénieur principal principal chez Intel Components Research Group, dans une interview à Reuters.

« Nous réduisons la longueur d’interconnexion et économisons de l’énergie, ce qui la rend non seulement plus rentable, mais aussi plus performante », a-t-il déclaré.

The English, Chinese, Japanese, Arabic, and French versions are automatically generated by the AI. So there may still be inaccuracies in translating, please always see Indonesian as our main language. (system supported by DigitalSiber.id)